# A 'greedy' channel router

# Ronald L Rivest and Charles M Fiduccia

A 'greedy' channel-router is presented. It is quick, simple and effective. It always succeeds, usually using no more than one track more than required by channel density. It may be forced in rare cases to make a few connections 'off the end' of the channel, in order to succeed. It assumes that all pins and wiring lie on a common grid, and that vertical wires are on one layer, horizontal on another. The greedy router wires the channel left-to-right, column-bycolumn, wiring each column completely before starting the next, Within each column the router tries to maximize the utility of the wiring produced, using simple, 'greedy' heuristics. It may place a net on more than one track for a few columns, and collapse the net to a single track later on, using a vertical jog. It may also use a jog to move a net to a track closer to its pin in some future column. The router may occasionally add a new track to the channel, to avoid getting stuck.

integrated circuits, layout, routing

Introduced in 1971<sup>1</sup>, channel routing has become a very popular method of routing integrated circuits<sup>2-8</sup>. Typically, the wiring area is first divided into disjoint rectangular channels. A global router then determines which channels each net traverses. Finally a channel router computes a detailed routing for each channel. This approach is effective because it breaks down the overall problem into a number of simpler problems and simultaneously considers all nets traversing each channel.

The general channel-routing problem has been proven NP- Complete 9-12, although algorithms exist for highly-restricted cases 10,13-16. A slightly different wiring model permits one to come within a factor of two of channel density 17. Useful methods also exist for computing lower bounds on channel widths 18,19. These results highlight the need for good practical heuristics.

The algorithm presented here exploits a novel control structure: a left-to-right column-by-column scan of the channel, where the router completes the routing for one column before proceeding to the next. In each column the router acts in a 'greedy' manner trying to maximize the utility of the wiring produced.

Our work is an extension of Alford's<sup>20</sup>, who also considered a left-to-right scan of the channel. His router did not guarantee success (because it did not allow nets to occupy more than one track in any column), ran quite slowly, and produced poorer results than our 'greedy' algorithm.

Kawamoto and Kajitani<sup>7</sup> use a similar column-by-column approach, but not in left-to-right order. They also assume (as we do not) that between adjacent columns there is enough room to wire an arbitrary permutation.

The following paragraphs define what we mean by a

MIT Laboratory for Computer Science, Cambridge, MA 02139, USA and GE Research and Development Center, Schenectady, NY 12301, USA

channel routing problem and its solution. A channel-routing problem is specified by giving

- A channel-length  $\lambda$ . Most of the routing will lie within the channel whose left end is at x = 0 and right end is at  $x = \lambda + 1$ , on the vertical columns at x-coordinates  $1, \ldots, \lambda$ , although columns outside the channel may also be used.

- Top and bottom connection lists  $T = (T_1, \ldots, T_{\lambda})$  and  $B = (B_1, \ldots, B_{\lambda})$ .  $T_i$  (respectively  $B_i$ ) is the net number for the pin at the top (respectively bottom) of the *i*-th column (at x = i), or is 0 if no such pin exists.

- The left and right connection sets, L and R, specifying which nets must connect to the right and left ends of the channel. They are sets since we assume that a net need connect at most once to an end of the channel, and that the relative ordering of such connections may be chosen by the channel router.

A solution to a channel-routing problem specifies

- The channel width w the number of horizontal tracks used. These tracks are at y-coordinates 1,..., w. A channel router tries to minimize w.

- For each net n, a set of connected horizontal and vertical wire segments whose endpoints are grid points (x, y) with  $1 \le y \le w$ , except that segments with endpoints (i, 0) or (i, w + 1) must be included if  $T_i = n$  or  $B_i = n$ . Endpoints with x < 1 or x > w are legal but should be avoided. A net in L (respectively R) must have a segment touching the line x = 0 (respectively  $x = \lambda + 1$ ). Two segments in the same direction are on the same layer, so they may not touch if they are for different nets. Two segments for the same net in different directions that touch at a grid point are said to be connected by a contact or via at that point. If the segments were for different nets we would have a crossover.

The channel density of a particular channel routing problem is defined to be the maximum number of nets which have pins on both sides of the line  $x = \alpha$ , for any  $\alpha$ . We do not count nets all of whose pins lie on a single vertical line. The channel density is a lower bound on the width of any solution to that channel-routing problem.

If its 'conflict graph' contains cycles, a channel-routing problem may be unsolvable within the channel, for any w (eg  $\lambda = 2$ , T = (1, 2) and B = (2, 1)). Such problems can always be solved by using columns outside the channel.

The following factors are often used to evaluate the quality of a successful solution (in a typical order of priority): its width w, the number of columns off the end it uses, its total wire-length, and the number of vias it uses.

# **ROUTING ALGORITHM**

The greedy router scans the channel in a left-to-right, column-by-column manner, completing the wiring within a given column before proceeding to the next. In each column the router tries to maximize the utility of the wiring produced, in a simple 'greedy' manner.

Its first step in a column is to make connections to any pins at the top and bottom of the column. These connections are minimal; no more vertical wiring is used than is needed to bring these nets safely into the channel, to the first track which is either empty or contains the desired net.

The second step in a column tries to free as many tracks as possible by making vertical connecting jogs that collapse nets that currently occupy more than one track. This step may complete the job of bringing a connection from a pin over to a track that its net currently occupies (step 1 might have stopped at an intermediate empty track).

The third step tries to shrink the range of tracks occupied by nets still occupying more than one track, so collapsing these nets later will be less of a problem. Since freeing up tracks has high priority, jogs made here have priority over jogs made in the next step.

The fourth step makes preference jogs that move a net up if its next pin is on the top of the channel, and down if its next pin is on the bottom. The router chooses longer jogs over shorter ones if there is a conflict. This tends to maximize the amount of useful vertical wiring created. These jogs are effective at resolving upcoming conflicts, even though no explicit consideration of these conflicts is made.

The fifth step is only needed if a pin could not be connected up in step one because the channel is full. Then the router adds a new track to the channel between existing tracks, and connects the pin up to this track. The old tracks are renumbered.

When the processing for a column is complete, the router extends the wiring into the next column and repeats the same procedure. The following paragraphs make precise the algorithm just sketched.

The input for the greedy router consists of

- a specification of a channel-routing problem

- three non-negative integer parameters: initial-channelwidth, minimum-jog-length, and steady-net-constant

The greedy router begins with the initial-channel-width given. A new track is added whenever the current channel-width becomes unworkable. The router does not begin over when a new track is added, so different initial widths may give different results. Good results are usually obtained with initial-channel-width just less than the best final channel width. One can run the router several times, with initial-channel-width set initially to the channel density and increased by one each time.

The router will make no jogs shorter than minimum-joglength. A higher setting reduces the number of vias and thus produces more acceptable solutions, while a lower setting tends to reduce the number of tracks used. The best results are obtained with a setting of about w/4, where w is the best channel width obtainable. By running the router 2-4 times with different initial parameter settings we quickly determined the best solution obtainable.

Let H(n) denote the highest column k for which  $T_k = n$  or  $B_k = n$  (except that  $H(n) = \lambda + 1$  if  $n \in \mathbb{R}$ ). We say a net n has its last pin in column k if H(n) = k and that it has its last pin by column k if  $H(n) \le k$ .

When routing a given column, the greedy router classifies each net which has a pin to the right as either rising, falling, or steady. A net is rising if its next pin after the current column will be on the top of the channel (say in column k), and the net has no pin on the bottom of the channel

before column k + steady-net-constant. Falling nets are defined similarly. Steady nets are the remaining nets. We typically use a value of 10 for steady-net-constant. A larger value reduces the number of times a multipin net changes tracks.

The fundamental data structure for this router is the set Y(n) for each net n of tracks currently occupied by net n. Each track is denoted by its y-coordinate, so Y(n) is a subset of  $\{1, \ldots, w\}$  for each n. If  $Y(n) = \phi$  (the empty set), the net is not currently being routed (i.e. we have not yet reached the first column in which net n has a pin, or we have passed the last column in which net n has a pin and have completed all the routing for net n). Otherwise, suppose  $Y(n) = \{y_1, \dots, y_k\}$  when the router is working on column i. Then each point  $(i, y_1), \ldots, (i, y_k)$  is a dangling end of some wiring already placed for net n. Exactly one such dangling end is listed in Y(n) for each connected piece of wiring already placed for net n. The router is obliged to connect together these dangling ends eventually so that each net is finally implemented by a single connected piece of wire. When extending the routing from column i to column i + 1, horizontal wiring will be used in every track y for which  $y \in Y(n)$  for some n and either |Y(n)| > 1 (the dangling ends have yet to be connected together) or the last pin for net n occurs after column i.

We define a net to be split at any time that |Y(n)| > 1. We also call a split net collapsible, since we may be able to collapse it down to a single track (or zero tracks if we have passed the last pin for the net) by making an appropriate connecting jog.

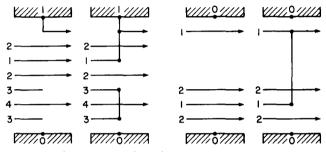

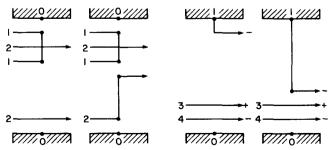

We illustrate the operations of the router using a set of before/after figures for each step. These figures describe what happens in a single column, and should be interpreted as follows. Nets entering a column from the previous column are shown extended up to the current column. If the net has pins to the right of this column, the net is shown extended towards the next column with an arrowhead. Otherwise (if the net has no pins to the right), no arrowhead is shown. A '+', '-', or '+/-' may be shown next to an arrowhead to denote rising, falling, or steady nets.

### **GREEDY ROUTER**

Let w denote the current channel width (initially w = initial-channel-width).

# Assign tracks to nets at left end

For each net n in L give n a distinct value for Y(n) (ie a distinct track in the range  $1, \ldots,$  initial-channel-width on which to enter the channel from the left end.) Put the rising nets above the steady nets above the falling nets and generally group the nets at the centre of the channel.

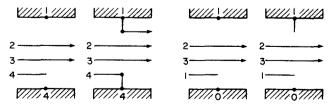

Figures 1 (left) and 2 (right). Figure 1. Adding to  $Y(T_i)$  or  $Y(B_i)$ . Figure 2. n is not routed to the nearest track in Y(n) if there is a nearer empty track

136 computer-aided design

### Route channel from left to right

For each column i, for  $i = 1, 2, \ldots$ , until  $i \ge n$  and no split nets remain to be collapsed do the following.

# Step 1: Make feasible top and bottom connections in minimal manner

If  $T_i$  or  $B_i$  is nonzero, bring in that net if possible to the nearest possible track which is either empty or already assigned to this net, by running a vertical wire from the edge of the channel to the desired track, and adding that track to  $Y(T_i)$  or  $Y(B_i)$ , (Figure 1). Note that a net n is not routed to the nearest track in Y(n) if there is a nearer empty track — leaving n temporarily assigned to an additional track (Figures 2, 3). Also note that a new net

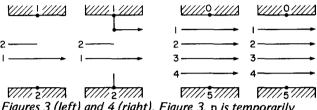

Figures 3 (left) and 4 (right). Figure 3. n is temporarily assigned. Figure 4. A new net cannot be brought into a full channel

cannot be brought into a full channel in this step (but see step 3) (Figure 4). If  $T_i$  and  $B_i$  are both nonzero, try to bring in both nets but in  $T_i \neq B_i$  and the vertical segments would conflict (overlap) then just bring in the net which can be brought in with the least wire, and leave the other net to be brought in the third step (Figure 5). As special

Figures 5 (left) and 6 (right). Figure 5. Least wire net is brought in. Figure 6. A vertical wire is run from top to bottom

case, if there are no empty tracks, and net  $T_i = B_i \neq 0$  is a net which has connections in this column only, then run a vertical wire from top to bottom of this column (Figure 6).

# Step 2: Free as many tracks as possible by collapsing split nets

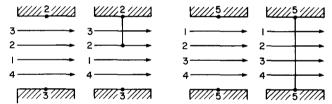

Add vertical segments in this column to collapse split nets in a pattern that will create the most empty tracks for use in the next column. Define a collapsing jog to be a piece of vertical wire which connects two tracks holding the same net without crossing another track holding that net. (So each split net n generates |Y(n)| - 1 such jogs.) Define a pattern to be any set of collapsing jogs for which jogs for different nets do not overlap and for which no jogs overlap any vertical wiring placed in the first step. The number of such patterns to consider may be exponential in the number of collapsing jogs there are to consider. Find the pattern which creates the most empty tracks by a small but complete combinatorial search (Figures 7 and 8). A pattern will free up one track for every jog it contains, plus one additional track for every net it finishes. The pattern finishes a net n if it totally connects up the dangling ends for n and n has its last pin by column i. Resolve any ties

Figures 7 (left) and 8 (right), Figure 7. The pattern is found, . . Figure 8, which creates the most empty tracks

between patterns that free up the most tracks by choosing the pattern which leaves the outermost uncollapsed split net as far as possible from the channel edge. If necessary consider the second outermost such net, etc (Figure 9). Resolve any remaining ties by choosing the pattern with largest sum of jog lengths (Figure 10). Add appropriate

Figures 9 (left) and 10 (right). Figure 9. Consider the outermost uncollapsed split nets, Figure 10. Choose the pattern with the most jog length

vertical wiring for each jog in the winning pattern, and for each such jog which connects a track  $y_1$  to a track  $y_2$  (assume  $y_1 < y_2$ ) for some net n, delete  $y_1$  from Y(n). This is an arbitrary choice that might get modified in the next two steps. Note that this step will typically collapse a net that was temporarily brought in to an empty track in the first step when that net had a previously assigned but more distant track.

#### Step 3: Add jogs to reduce the range of split nets

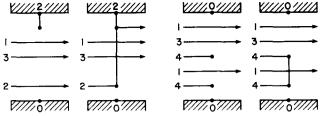

For each uncollapsed split net (ie for each net n with  $Y(n) \ge 2$ ) try to reduce the range of tracks assigned to the net by adding vertical jogs that have the effect of moving the net

- from the maximum track in Y(n) to the lowest possible empty track

- from the minimum track in Y(n) to the highest possible empty track (Figure 11)

Because of step 2, no collapsing will occur, but the difficulty of collapsing the remaining split nets may be

Figures 11 (left) and 12 (right), Figure 11, Highest possible empty track, Figure 12, Close to its target edge

reduced. Make no jogs which are shorter than minimum-jog-length or which would be incompatible with vertical wiring already placed in this column by previous steps. If a jog for net n is made from track  $y_1$  to track  $y_2$ , replace  $y_1$  by  $y_2$  in Y(n).

#### Step 4: Add jogs to raise rising nets and lower falling nets

Consider all the unsplit (ie |Y(n)| = 1) rising and falling nets being routed in order of decreasing distance from their track  $y \in Y(n)$  to their target edge (eg. the upper edge of the channel for rising nets). Try to add a vertical jog to move that net to an empty track which is as close as possible to its target edge, (Figure 12). Make no jogs which are shorter than minimum-jog-length or which would be incompatible with vertical wiring already placed in this column by previous steps. If a jog for net n is made from track  $y_1$  to track  $y_2$  replace  $y_1$  by  $y_2$  in Y(n).

# Step 5: Widen channel if needed to make previously not feasible top or bottom connections

If a net  $T_i$  or  $B_i$  could not be brought in to a track in the first step, create a new track for this net and bring the net in to this track. Place this track as near the centre of the channel as possible between existing tracks, subject only to the constraint that desired connection to the edge of the channel can be made (Figure 13). If the new track lies between tracks previously numbered k and k+1, all old tracks at y-coordinates k+1 and greater now have their y-coordinates retroactively increased by one, and all Y(n) referring to these tracks are appropriately modified. Add the new track to  $Y(T_i)$  or  $Y(B_i)$  as appropriate.

Figures 13 (left) and 14 (right). Figure 13. Connection to channel edge, Figure 14. Horizontal wiring

#### Step 6: Extend to next column

For each net n such that |Y(n)| = 1 and n has no pins after column i make Y(n) be the empty set. (The routing for these nets is now finished.) Then for each track y which is in Y(n) for some n, extend the dangling end for net n along track y into column y + 1 with appropriate horizontal wiring. (Figure 14).

This completes the description of the greedy router. The router will always complete the routing successfully, although it may use a few columns beyond the natural right end of the channel.

The algorithm takes about 10 s on a DEC KA-10 for moderate sized channels. The implementation was simple — about 15 pages of LISP code, counting 10 pages for I/O and initialization.

# DISCUSSION

This algorithm is the result of long series of experimentation and evaluation of variations on the basic idea of scanning

down the channel from left to right and routing everything as you go.

By minimally connecting a net in the first step above, we separate the tasks of connecting up a pin and of deciding to use a column to jog all the way over to a track the net may already be on. The second step makes this latter decision; it might turn out that another such collapsing pattern frees up more tracks.

When collapsing nets, the router tries to free the most tracks because it is hard to achieve optimal routings if nets are allowed to occupy more than one track for very long. We observed that in general it is very difficult to collapse a net in a track just next to the channel edge. This is because other nets must cross this track to enter the channel. So the collapsing algorithm will favour patterns that collapse these difficult nets.

The use of combinatorial search for the net collapsing phase was found to be acceptably fast. There were never more than four split nets in our examples. A dynamic programming approach can be used instead if it is desired to avoid exponential worst-case running times.

We were surprised to find that the search step works so well, since it is very simple and takes no particular notice of forthcoming conflicts. Our initial implementation tried first to resolve forthcoming conflicts in order, and then to jog the other nets as much as possible in appropriate directions. The success of the current variation seems to be because it tries to jog nets in tracks near the edges of the channel first — these are the most difficult places to move a net from — and also because the router will tend to maximize the amount of useful vertical wiring created.

One good feature of the greedy router is that its control structure is flexible and robust: it is easy to make variations in the heuristics employed to achieve special effects or to rearrange priorities. The particular algorithm presented here is merely our best suggestion based on our experimental evidence. Other variations may turn out better in other situations. We have also considered a gridless variation where the track-to-track spacing can be reduced if a pair of adjacent tracks does not have contacts next to each other in some column. This variation uses more intelligence when selecting the jogs to make in a given column. It is also easy, for example, to restrict jogs for a net to those columns for which it has a top or bottom connection, etc. Another variation we have not yet tried is to scan outwards from a column of maximum density instead of using a left-to-right scan; we expect this variation may prove to be valuable in practice as well. We are not very sure how one should best order the nets in L at the beginning. How should a set of rising nets be ordered?

One extension that is worth noting in particular is that it is not too difficult to modify the router to handle the notorious switchbox problem — where a channel has a fixed length and width and terminals fixed on all four sides<sup>11</sup>. Two MIT students, Kim Koschella and David Christman, have performed this modification; their results are reported in Koschella's BS thesis and their program is currently used in the MIT 'PI' system<sup>21,22</sup>.

### **EXPERIMENTAL RESULTS**

We present three sorts of experimental results

- data on five chips routed at GE using previous algorithms

- data on Deutsch's difficult example

- data on program-generated standardized<sup>22</sup> test examples

We considered five chips at GE that were designed using a

138 computer-aided design

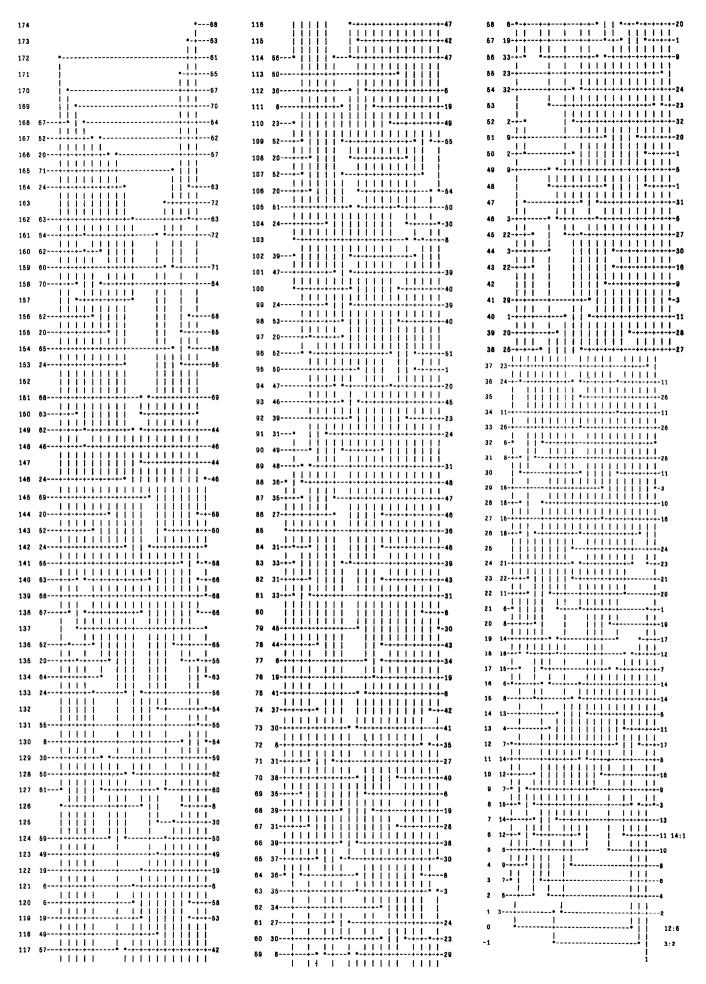

Figure 15. Deutsch's difficult example

polycell approach. All together they contained 26 channels, with an average channel density of 16.500, and a range of densities from 12–43. The greedy algorithm was able to route all of these channels successfully, with an average channel width of 16.654 (ie it routed 22 of the 26 channels using a number of tracks exactly equal to the channel density, and routed 4 of them using one more track than the channel density). This represents an average of an increase of 0.93 per cent over channel density. The previous router used at GE averaged an increase of roughly 12 per cent over channel density for these problems.

We tested the greedy router on the difficult example of Deutsch<sup>4</sup> (see Figure 15). This problem has a channel density of 19. To our knowledge no completely automatic algorithm has produced a routing in 19 tracks. Yoshimura and Kuh report an algorithm which achieved 20 tracks on this problem<sup>23</sup>. The greedy algorithm also produced a routing in only 20 tracks (although it did use more vias). The routing is given in the Appendix.

A paper<sup>22</sup> contains a standard set of bench-mark channel-routing problems, described by a program that generates them. We ran the greedy router on many benchmark channels taken from this paper, and were generally unable to improve by hand any of the routings found.

#### **ACKNOWLEDGEMENTS**

We should like to thank Dan Schweikert, David Deutsch, Ernest Kuh, Phil Lewis, James Rumbaugh, Flavio Rose, Ron Pinter, Charles Leiserson, Alan Baratz, and Seth Alford for helpful discussions, information and/or critical comments on an early draft of this paper.

#### REFERENCES

- 1 Hashimoto, A and Stevens, J 'Wire routing by optimizing channel assignment within large apertures' *Proc. 8th Des. Aut. Worksh.* IEEE (1971) 214–224

- 2 Kernighan, B, Schweikert, D and Persky, G 'An optimal channel-routing algorithm for polycell layouts of integrated circuits' *Proc. 10th Des. Aut. Workshop* IEEE (1973) 50–59

- 3 **Hightower**, **D** 'The interconnection problem: a tutorial' *Comput*. (April 1974) 18-32

- 4 Deutsch, D N 'A "Dogleg" channel router Proc. 13th Des. Aut. Conf. IEEE (1976) 425-433

- 5 Asano, T, Kitahashi, T and Tauaka, K 'On a method of realizing minimum-width wiring' *Electron. Commun. Japan* Vol 159-A, No 2 (1976) pp 29-39

- 6 Persky, G, Deutsch, G D and Schweikert, D 'LTX a minicomputer-based system for automated LSI layout' J. Des. Aut. Fault-Tolerant Comput. (May 1977) pp 217–255

- 7 Kawamoto, T and Kajitani, Y 'The minimum width routing of a 2-row 2-layer polycell-layout' *Proc.* 16th Des. Aut. Conf. IEEE (1979) pp 290-296

- 8 Rivest, R L 'The 'Pl' (placement interconnect) System' Proc. 19th Des. Aut. Conf. Las Vegas (1982)

- 9 Garey, M and Johnson, D Computers and intractability: a guide to the theory of NP-completeness Freeman (1979)

- 10 La Paugh, A 'Algorithms for integrated circuit layout: an analytic approach' *PhD Thesis* MIT Laboratory for Computer Science Report TR-248 (November 1980)

- 11 **Soukup, J** 'Circuit layout' *Proc. IEEE* Vol 69 No 10 (October 1981) pp 1281–1304

- 12 Sahni, S and Bhatt, A 'The complexity of design automation problems' *Proc. 17th Des. Aut. Conf.* IEEE (June 1980) pp 402–411

- 13 Dolev, D, Karplus, K, Siegel, A, Strong, A and Ullman, J 'Optimal wiring between rectangles' *Proc. 13th Ann. ACM Symp. Theory Comput.* (May 1981) pp 312–317

- 14 Leiserson, C and Pinter, R 'Optimal placement for river routing' *Proc. CMU Conf. VLSI Syst. Comput.* Computer Science Press (1981) pp 126–143

- 15 Pinter, R. 'Optimal routing in rectilinear channels' 'Proc. CMU Conf. VLSI Syst. Comput. Computer Science Press (1981) pp 160–177

- 16 Tompa, M 'An optimal solution to a wire-routing problem' *Proc. 12th Ann. ACM Symp. Theory Comput.* (April 1980) pp 201–210

- 17 Rivest, R L, Baratz, A E and Miller, G 'Provably good channel-routing algorithms' *Proc. CMU Conf. VLSI Syst. Comput.* Computer Science Press (1981) pp 153–159

- 18 Brown, D and Rivest, R L 'New lower bounds on channel-width' *Proc. CMU Conf. VLSI Syst. Comput.* Computer Science Press (1981) pp 178–185

- 19 Leighton, T 'New lower bounds for channel-routing' Forthcoming

- 20 Alford, S 'DYCHAR: a channel router which uses dynamic channel assignment' MIT Bachelor's thesis. (May 1980)

- 21 Koschella, J 'A placement/interconnect channel router: cutting your PI into slices' *Bachelor's thesis* MIT Department of Electrical Engineering and Computer Science Press (May 1981)

- 22 Rivest, R L "Benchmark' channel-routing problems' Forthcoming

- 23 Yoshimura, T and Kuh, E 'Efficient algorithms for channel-routing' UC Berkeley Electron. Research Lab. Memo. No. M80/43 (August 1980)

# APPENDIX. DEUTSCH'S 'DIFFICULT EXAMPLE'

Initial channel height = 18 Jog threshold = 6 Using fixed grid No centering tracks Reversing channel Density = 19

Density = 19

Time = 19.20722 s

2 extra columns

17 wide spacing between tracks

20 tracks used

Wire length = 5 381

Number of vias = 403

Number of vias - 40.

140 computer-aided design