Proceedings of the Fifth Workshop on Multithreaded Execution, Architecture and Compilation

# **MTEAC-5**

## December 1, 2001 -- Austin, Texas In Association with the 34<sup>th</sup> International Symposium on Microarchitecture

## **PROGRAM CO-CHAIRS**

Walid Najjar, University of California, Riverside

Antonio González, Universitat Politecnica de Catalunya

Dean Tullsen, University of California, San Diego

## PROGRAM COMMITTEE

| Willem Böhm, Colorado State<br>University | Eric Rotenberg, <i>North Carolina State</i><br><i>University</i> |

|-------------------------------------------|------------------------------------------------------------------|

| Michel Dubois, University of Southern     | Andre Seznéc, IRISA/INRIA                                        |

| California                                | John Shen, Intel Corporation                                     |

| Guang Gao, University of Delaware         | Josep Torrellas, University of Illinois,                         |

| Sebastien Hily, Intel                     | Urbana-Champaign                                                 |

| David Kaeli, Northeastern University      | Jordi Tubella, Universitat Politecnica de                        |

| Steve Keckler, University of Texas        | Catalunya                                                        |

| Artur Klauser, Intel Corporation          | Mateo Valero, Universitat Politecnica de Catalunya               |

| Mario Nemirovsky, Netmetrica, Inc.        | Theo Ungerer, University of Karlsruhe                            |

| Yale Patt, The University of Texas at     |                                                                  |

| Austin                                    | Pen-Chung Yew, University of<br>Minnesota                        |

Fifth Worksherr on Multithreaded Execution, Archivecture and Comilisiden

##

## Decamba 1, 2, 2000 Paras In Amori 2, 2000 Paras 34<sup>th</sup> International Synt

enters, University of C

Antoria Camateta, Umiverne e e e e e e e e e e e

Days Tutkers, University, of C. J.F. Ster. 141, 1990

## 331 Physics Contractor

Million Colorado Stati General 2

Michael («Lonais, University of <sup>19</sup>11) Calificatio

Constity II von Winteenbergelij of Exc. In Roto omber redek Jennel

Davin Candi, Northeasturn Universit Steves Keelder, Universiticof Trans Artur Klauser, Intel Corporatico Mano Nontrovský, Anisteitettov, Ea. Vato Pati, The University of Trans at Advilla

E. v. Rotonburg, Nath Carstine State Deversity

ARMINAZIAL DARDAG FARMARIA

ist a Shan, istel Caponilian

anna an ann Carl Cheersator Politica an sa 19 Teachada

Norther - Marc, Whitemester Paliticenica

Paris Adjonan International Narismin Paris International American Minnesolui

## **MTEAC-5**

## WORKSHOP PROGRAM

## Session I:

Message-Passing for the 21<sup>st</sup> Century: Integrating User-Level Networks with SMT, Mike Parker, AI Davis, Wilson Hsieh, University of Utah.

A Binary Translation System for Multithreaded Processors and its Preliminary Evaluation, Kanemitsu Ootsu, Takashi Yokota, Takafumi Ono, Takanobu Bab, Utsonomiya.

The Predictability of Computations that Produce Unpredictable Outcomes, Tor Aamodt, Andreas Moshovos, Paul Chow, University of Toronto.

## Session II:

Hierarchical Multi-threading for Exploiting Parallelism at Multiple Granularities, Mohamed M. Zahran, Manoj Franklin, *University of Maryland*.

Basic Mechanisms of Thread Control for On-Chip-Memory Multi-threading Processor, Takanori Matsuzaki, Hiroshi Tomiyasu, Makoto Amamiya, Kyushu University.

Maximizing TLP with Loop-Parallelization on SMT, Diego Puppin (Massachusetts Institute of Technology), Dean Tullsen (University of California, San Diego).

## Session III: Keynote Address

Speculative Multithreading: From Multiscalar to MSSP, Guri Sohi, University of Wisconsin, Madison.

## Session IV:

Branch Prediction in a Speculative Dataflow Processor, Bradley C. Kuszmaul, Dana S. Henry, Yale University.

A Study of Compiler-Directed Multithreading for Embedded Applications, Anasua Bhowmik, Manoj Franklin, Quang Trinh, University of Maryland.

Prefetching in an Intelligent Memory Architecture Using a Helper Thread, Yan Solihin, Jaejin Lee, Josep Torrellas, University of Illinois, Urbana-Champaign.

## Session V: Keynote Address

Multithreading for Latency, John P. Shen, Intel Corporation.

## MASOC - DOWNER

#### ANG MARK

Wessage-Parsing for the 21" Centre of the Content of the Content of Networks with Mile Mile 2007

A Biancel Contell Constant for Mina Contellination of Contention and Its Provintinary Brandword Content Debug Dilantic Inc. 2011 (2001) State Polynetic Contention

The ProductsPity of Computations with the Product I of Admod. Nucleus Mean and Paul Chave On the

## W. INARAD Z

Naraddad Bulli-threading for S 199

Maxtmixing TLP with Loop-Parateurs and SMT, Dego Poppin (Massaussells institute of Technology, Deen Tulton (University)

## Render Address

## A DOUBLE

Branch Prautation in a Specification and the Ausoarcor, Bradley C. Kuszmaul, Dani S. Hanav, Yawainingraity

A Study of Compiler-Directed Merice and a Embedded Applications, Anseus, Shown? Manoi Franklin, Quand Test

Profetobility in an Infelfigent/Manary Are that a Using a Heiper Thread and collain, Jaada Lee, Josep Tomolas, University of Witchiele Arean-Chargeniew.

#### Sussion V. Kerroole Auldrass

Nukhtersetting för Läternig, Solle 2. Stelle – Solle för

## Message-Passing for the 21st Century: Integrating User-Level Networks with SMT

Mike Parker, Al Davis, Wilson Hsieh School of Computing, University of Utah

#### Abstract

We describe a new architecture that improves message-passing performance, both for device I/O and for interprocessor communication. Our architecture integrates an SMT processor with a userlevel network interface that can directly schedule threads on the processor. By allowing the network interface to directly initiate message handling code at user level, most of the OS-related overhead for handling interrupts and dispatching to user code is eliminated. By using an SMT processor, most of the latency of executing message handlers can be hidden. This paper presents measurements that show that the OS overheads for message-passing are significant, and briefly describes our architecture and the simulation environment that we are building to evaluate it.

## **1** Introduction

The same VLSI technology forces that are driving processor interconnect are also having an impact on I/O architectures. As clock frequencies increase, high capacitance processor and I/O buses cannot keep pace. These buses, on and off chip, are being replaced by point-to-point links. I/O interfaces are starting to look much more like message-passing networks, as is evidenced by recent standards such as InfiniBand[25] and Motorola's RapidIO[27]. Communication over these point-to-point I/O networks can be viewed as low-level message-passing, where queries are sent to devices and responses are received from devices. Since technology trends force the hardware to use point-to-point links, there is an interesting opportunity to expose communication directly to user-level software through a message-passing interface. By looking at this opportunity from a systems point of view (from user-level software down to the hardware), we anticipate that we can dramatically reduce the costs for both processor-to-processor and processor-to-IO message-passing.

Our architecture for addressing this problem consists of the following combination of ideas:

- An SMT processor allows the overhead of message handlers to be effectively hidden.

- A network interface that supports user-level access can be tightly coupled to the CPU to avoid the overhead and latency of slower I/O buses. In addition, the network interface can directly dispatch user-level threads on the SMT processor, which eliminates OS involvement in the common case

- A message cache buffers incoming messages so that they can be accessed quickly by the processor, and acts as a staging area for outgoing messages.

- A zero-copy message protocol allows messages to be delivered directly to user-space without copying.

Not all of these ideas are new. For example, previous research has explored the use of user-level network interfaces[3,9,11,13,18]. However, this specific combination of features is unique, in that it exposes interrupts directly to user-level programs. The important aspect of our architecture lies in its support for user-level messaging (for Loth interprocessor communication and I/O) in a general-purpose operating system with small modifications to an SMT processor.

The combination of features in our architecture should reduce message handling overheads dramatically, without requiring gang-scheduling or forcing a change of the message notification model that is seen by the user-level software. The SMT processor, originally targeted to hide message latency, makes it possible to overlap computation and communication without adding a secondary communication processor. The combination of a zero-copy protocol, a message cache, and user-level access to the network interface allows user code to communicate without the overhead of OS involvement or data copying. Finally, our integration of the network interface (NI) with the SMT allow the NI to communicate message arrival events back to the target thread without most of the overhead an interrupt-style notification would incur.

## 2 Message Notification Costs

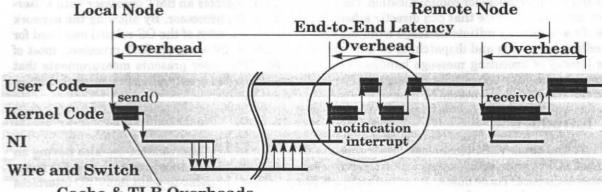

Figure 1 shows how a message send and receive may look from a single node point of view on a machine that uses a kernel-mode network interface and traditional interrupts for message arrival notification. Sends, receives, and notifications all make passes through operating system code. Since the operating system code is unlikely to reside in the cache, these system calls result in cache misses.

Cache & TLB Overheads

Figure 1: Anatomy of a message for a kernel-mode NI

User-level interfaces [3,9,11,13,18] and zero-copy protocols [5,7] significantly reduce the overhead of message sends and receives by eliminating operating system and copying overhead on the message send and receive sides. Notifications still have significant opportunity for optimization, as they remain the performance and scalability bottleneck in general multi-user environments. Polling for notifications consumes significant processor and memory resources, making them undesirable in a multiprogrammed system. Polling is especially poor for programs with irregular or unpredictable communication patterns. Interrupts in current architectures and operating systems are costly in terms of the number of processor cycles consumed to determine the cause of and handle the exception [12]. This makes them less than optimal for message notifications.

The components of an interrupt-style notification overhead include:

- processor pipeline flushing (due to the interrupt)

- serial instructions to get and save processor state

- · cache and TLB misses to bring in OS code and data to determine the cause of the interrupt

- · reading NI registers or data structures to determine which process should be notified

- posting the notification to the process via a signal or other such mechanism

- cache, TLB and context switch overhead to begin execution of the user-level notification (signal) handler

- a trap to return from the user-level handler back to the OS

- serial instructions to save processor state

- cache and TLB overhead to bring in OS code and data

- scheduler and context switch overhead to bring back in the original user process

- post kernel cache and TLB overhead to bring back in the user process's instructions and data

Using a refined version of Schaelicke's interrupt measurement work[22], we measured the overhead of servicing a network interrupt for a minimum sized packet. Under Solaris 2.5.1 on a 147-MHz Ultra 1, such an interrupt takes approximate 119 microseconds (17500 cycles) when user-level code is utilizing the entire L2 cache. The process of handling such an interrupt results in about 380 kernel-induced L2-cache misses. (Fewer misses may be observed in practice if the user-level code is not utilizing the entire L2 cache.) Assuming that each cache miss takes an average of approximately 270 ns to service[17], this accounts for about 103 microseconds or 87% of the interrupt processing time. The remaining 13% of the time is spent in flushing the pipeline after the interrupt and trap, carefully reading and saving critical processor state, querying the NI for information about the interrupt, and executing operating system code to determine how to deal with the interrupt. In addition to incurring the overhead of cache misses during an interrupt, the process that was running when the interrupt occurred could see up to another 380 L2 cache misses once it is re-scheduled after the interrupt to refill the cache with its working set.

7

L2-cache and TLB miss penalties unfortunately scale at memory speeds, as opposed to processor speeds. As a result, these overheads will become even more important as the memory gap widens. Optimizations to the OS and signalling system can reduce this overhead. However, reducing the number of cache misses and other overheads to get the OS penalty down below a few microseconds does not seem plausible. To make frequent notifications acceptable, the operating system's involvement must be significantly reduced or eliminated.

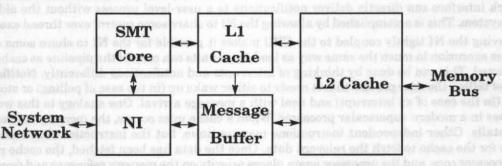

## **3** Architecture

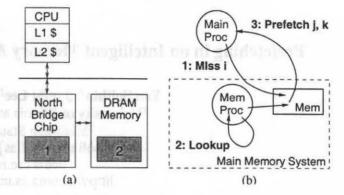

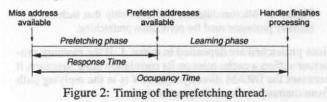

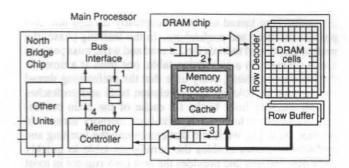

Notifications only become the bottleneck when the rest of the message-passing system is appropriately tuned. This section describes the system architecture, showing how it is optimized for efficient messaging, describes how notifications are delivered to the user-level process without kernel involvement, and walks through the path a one-way message takes though this architecture. Figure 2 shows a block-level view of the architecture.

Figure 2: Block-level diagram of our architecture

## **3.1 Components of the Architecture**

Using an SMT processor allows communication-related threads to run parallel to computationbased threads. Much of the overhead required to process sends, receives, and message arrival notification can be hidden by overlapping these functions with computation. Previous work has dealt with overhead by providing external communication processors[14,21]. These extra processors add to the overall latency and complicate the message-passing mechanism due to the additional overhead of communication between the computation and communication processor. The simultaneous nature of the SMT processor makes it possible to provide this overlap without requiring the use of an extra communications processor.

The message buffer acts as both a staging area for outgoing messages as well as a cache for incoming messages[23]. Messages may be composed directly in the message buffer for user-program written (PIO-style) transfers, or fetched from user memory for DMA-style transfers. Buffering outgo-

ing messages in the message buffer allows send data to be prefetched from memory and buffered before going out on the network. This buffering reduces the probability that the network will need to be stalled, tying up network resources, while waiting for outgoing message data to be supplied by the local memory subsystem.

Incoming messages are placed in the message buffer. The message buffer acts as a cache for incoming message data. As a message arrives, the message buffer invalidates corresponding cache lines in the L1 and L2 caches. Misses in the L1 cache result in concurrent lookups in both the L2 cache and the message buffer. In this way, the message buffer is similar to a victim cache to the L2 cache. When there is a cache hit in the message buffer, data is supplied directly to the L2 cache. This cache has a triple effect. First, it reduces overhead at the memory interface by saving the data two trips across the memory bus. Second, it keeps the data near the CPU, where it can be provided quickly on demand, thus reducing the overall end-to-end latency. Third, having a separate message cache avoids polluting the cache hierarchy because the processor's working set is not evicted by incoming messages.

A user-level accessible NI is used to reduce send and receive overhead. Having the network interface on the same die, possible in the System on a Chip (SoC) era, opens up possibilities to more tightly integrate it with the processor core, further reducing overhead and latency. Having the NI on die gives the processor access to it on a per cycle basis. This close coupling further reduces the overhead in getting information to and from the NI. Message sends and receives do not have to go out over slow and inefficient I/O buses. A zero-copy protocol[5,7] is used to eliminate copying overhead for received messages. The combination of user-level access to a closely coupled NI and the zero-copy protocol allow for efficient sends and receives.

## **3.2 User-level Notifications**

Part of the inefficiency of interrupt processing is due to the legacy view that interrupts are expected to be infrequent. In a fine-grained message-passing environment that uses interrupts for notifications, this is not the case. One of the contributions of this work is to provide a mechanism whereby the network interface can directly deliver notifications to a user-level process without the aid of the operating system. This is accomplished by allowing the NI to share some control over thread execution.

Having the NI tightly coupled to the CPU makes it possible for the NI to share some control over process execution in much the same way as load-store units can control the pipeline as cache misses are detected. This can be done by thinking of interrupts and notifications differently. Notifications are a way of telling the user process that it needs to either wake up (in the case of polling) or stop what it is doing (in the case of an interrupt) and deal with a message arrival. One analogy to this would be cache misses in a modern superscalar processor. When a cache miss occurs, the memory reference instruction stalls. Other independent instructions may continue, but the instruction that caused the miss waits for the cache to fetch the relevant data. Once the data has been fetched, the cache returns it to the processor core, and the processor again places priority on the memory reference and dependent instructions.

This basic idea can be extended to message arrival notifications. When a process reaches a point where it needs a message arrival notification, it can tell the hardware what specific process state to change (i.e., program counter or runability) when an arrival occurs. It can then continue processing until either the notification occurs, or it runs out of things to process. When the notification finally takes place, the hardware can redirect the user-level software to work on processing the message arrival.

To give the NI shared control over user processes, three mechanisms are available in our architecture.

• If a thread wishes to be notified when a message arrives, it can set a lock in a hardware synchronization lock table[24]. The NI can clear the lock bit upon message arrival, which releases the process to run again. If the associated thread is not currently in the CPU, the OS receives the notification, and sets the appropriate hardware state to notify the thread the next time it is scheduled.

- Just as an interrupt causes a current processor to asynchronously branch into a kernel level interrupt handler, the NI can cause a running user-level process to asynchronously branch to a notification handler.

- Upon message arrival, the NI can schedule a new thread on the SMT with a previously setup context. This new thread starts in either an unused context on the SMT or it can evict a running thread, according to OS policy. If no contexts are available, the NI would notify the OS, so that it could create the context and schedule it to run at a later time.

#### 3.3 The Journey of a Message

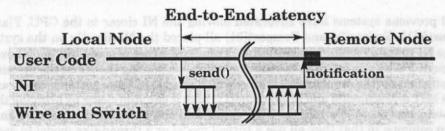

Figure 3 shows how a message may look in our architecture.

A user-level program that wants to send a message to a process on a remote processor first composes the message to be sent. Message control information is written into the message buffer. It includes information on how the message is to be handled on the remote end (where it will be placed and whether to notify the receiving process), a small amount of user-defined meta-data, and an optional local pointer to message data. The user process then directs the NI to send the message. The NI begins to prefetch message data from local memory into the message buffer if required, fills in information such as routing information, and begins streaming the message onto the wire. On the receive side, the message is placed directly in the address space of the receiving process by the NI. While the message is arriving, the NI places the message into the message buffer. As it fills cache lines in the message buffer, it acquires ownership of those cache lines though the L2-cache interface and sets up appropriate cache tags in the message buffer.

When an entire message arrives, the NI fills in a notification structure in the user process's memory space. It then determines which method should be used to notify the corresponding process of the message arrival. In the case of a blocked process waiting on a message arrival, the NI clears a lock bit in a synchronization table, which makes the corresponding thread runnable. The user-level process begins executing and handles the incoming message. In the case of an asynchronous branch or user-level interrupt, the SMT switches to an alternate program counter and stack. User-level code is then responsible for saving any of its own state as necessary before handling the notification. Finally, in the case of a created thread, the NI gives the SMT core minimal context, including a program counter, stack pointer, and a pointer to the notification structure. The SMT core begins executing at the given program counter.

In summary, we have presented an architecture that significantly reduces send, receive, and notification overhead. We have presented three separate user-level notification mechanisms, and have walked through the path a message takes in our architecture. The key features of the architecture are the following: SMT processors hide and tolerate message overhead and latency, send and receive overhead is reduced by a user-level network interface combined with efficient protocols, and notifications can be delivered directly to user-level without the overhead of an operating system.

10

## 4 Related work

Simultaneous Multithreading (SMT) architectures[8] have begun to see commercial attention. The SMT processor is targeted to tolerate latency and hide overhead by allowing one thread to process overhead or wait for a long latency operation while the execution of independent threads continues. SMT architectures promise the ability to simultaneously take advantage of both ILP and thread-level parallelism within a single processor core. This architecture helps pave the way to more efficient communication and synchronization of threads.

Dean Tullsen et al.[24] shows how extra lock and release hardware can be introduced to provide fine-grained synchronization for threads within the SMT processor. This efficient locking mechanism allows one thread to block on a hardware semaphore and be released by another co-operating thread quite efficiently. One of the suggested notification primitives in this paper extends some of the control over this hardware locking table to external events, such as message arrival notifications from the NI.

Several previous systems have advocated moving the NI closer to the CPU. Flash[14], Avalanche[23], Alewife[1], Shrimp[3], and Tempest[21] all placed the NI directly on the system memory bus. Moving the NI to the system bus significantly reduces the cost of accessing the NI over accessing it on a less efficient I/O bus. In addition to reducing overhead, placing the NI on the system bus allows these systems efficient access to coherency traffic, which several of these systems use to an additional advantage. The MIT J-Machine[6] and M-Machine[11] take it one step closer by bringing the NI directly onto the custom processor. Alewife, the J-Machine, and the M-Machine also have an interesting characteristic in common in that they all use a thread model or a thread-like model to deal with communication. Alewife uses a modified SPARC processor in an unconventional way to implement these threads.The J-Machine and M-Machine both build a custom processor to get the desired thread behavior. SMT processors now seem to be a natural way to achieve effective functionality of these machine with only minor modifications to CPU structure.

In many ways the architecture in this paper is similar to the M-Machine. Both take advantage of thread capable processors to hide message overhead, and both have forms of automatically dispatching threads when a message arrives. Our architecture differs from the M-machine in the following ways. Messages are received directly into a users address space via hardware, eliminating the need for trusted message handlers. Incoming messages are placed into a message buffer, or message cache, to avoid pollution of the processor's cache hierarchy. As a part of our work, we are evaluating the usefulness of this message-passing architecture both in the context of parallel processing and in the context of network-based IO. Finally this architecture is built upon modifications of upcoming SMT architectures.

Avalanche[23] placed the network interface on the system bus, keeping it close to the processor. This allowed it to participate in coherency traffic, and thus maintain a local network cache. The local cache enables the Avalanche network interface to supply network data to the processor more quickly than main memory. In addition, it avoids the overhead of wasting system bus bandwidth to transfer message data across the system bus twice; once on the way to main memory on message arrival, and once on the way back to the processor when the message is consumed.

For Hamlyn[5] Wilkes proposed sender-based protocols to reduce overhead. Having the sender manage its destination buffers implies that data can be easily and effectively received directly into the receiver's process space. Avalanche also used a sender-based messaging protocol (DDP)[7] to reduce overhead. Sender-based protocols allow simple and efficient hardware to place incoming messages directly into the receive process's address space. This avoids kernel involvement on receives. Unlike Hamlyn and DDP, the sender-based portion of the protocol in this work uses virtual addresses in combination with an NI TLB to remove restrictions on receive buffers.

Active Messages[10] embed a message handler in the header of a message. When a message arrives, the message handler is executed to handle the payload of the message. Though it is not specifically a goal of this work, the architecture described here would support Active Messages rather well. A thread waiting for a message could immediately jump to the handler code in the header without the penalty of an interrupt and without interfering with the currently running thread. If messages are received directly into a message cache, then this handler code could potentially execute directly out of the message cache, also saving the cache overhead of bringing in conventional handler code. Illinois Fast Messages[20] is effectively a platform independent implementation of Active Messages.

U-Net[9] reduces communication overhead and latency by virtualizing the network interface. The local process communicates with the network interface by placing and picking up message packets from per-process send and receive queues. U-Net suggests placing a TLB in the network interface to avoid the added restriction of fixed pinned pages. The architecture in this paper also gives the NI access to a TLB to allow sends and receives to be handled in user-space.

#### 5 Conclusion

SMT allows important computation to continue while interprocessor communication and I/O processing and communication overhead is handled in the background. Since message latency is similar to memory latency, one way of viewing this work is using an architectural technique for hiding memory latency to hide message latency. Conversely, we can view our work as generating more parallelism for SMT processors from I/O and parallel workloads.

To evaluate this architecture, we are extending LRSIM[22] to accurately model an SMT processor and adding a model of our network interface. LRSIM is based on RSIM[19], and has already been extended to include accurate I-cache, memory and I/O architecture models. The simulator includes a fairly complete NetBSD based kernel that will be extended to handle the SMT processor (all kernel operations are fully simulated). The simulator runs unmodified Solaris binaries. For our evaluations, we will model a 2-5 GHz 4-8 thread SMT that can issue 8-16 instructions per cycle. L1 instruction and data caches will be 32KB to 128 KB each, and the L2 Cache will be 4-16MB. The system network bandwidth modeled will range from 4Gb/s to 32Gb/s. Disk controllers, LAN interfaces (i.e., Ethernet), and other I/O devices will hang off the system network. There are a few open issues in our design:

- It remains unknown how much send side buffering will be optimal. Too little buffering could lead to too many bubbles in the network fabric. Too much could lead to increased message latency. For the purposes of this design, the amount of buffering will be user configurable.

- The point at which DMA becomes more efficient than PIO needs to be characterized for this . architecture. Though it has been characterized for previous systems, the break-even point on our architecture may be different as PIO can overlap computation on the SMT processor.

- The relative performance of each of the notification mechanisms needs to be characterized.

The results from the simulations will be compared with existing and proposed systems to assess the benefits of our architecture.

## Acknowledgements

We thank Lambert Schaelicke for his help in understanding and extending his interrupt measurement techniques. We also thank Lambert, John Carter, Katie Parker, and Greg Parker for help in reviewing this paper. This work was sponsored in part by DARPA and AFRL under agreement number F30602-98-1-0101 and DARPA Order Numbers F393/00-01 and F376/00. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official polices or endorsements, either express or implied, of DARPA, AFRL, or the U.S. Government.

## References

- Anant Agarwal, et al. The MIT Alewife Machine: Architecture and Performance. In Proceedings [1] of the 22nd Annual ISCA, 1995, pp. 2-13.

- Mark Birnbaum and Howard Sachs. How VSIA Answers the SoC Dilemma. IEEE Computer, [2] 32(6):42-50.

- [3] Matthias A. Blumrich, et al. Virtual Memory Mapped Network Interface for the SHRIMP Multicomputer. In Proceedings of the 21st Annual ISCA, April 1994, pp. 142-153.

- [4] Doug Burger. Billion-Transistor Architectures. IEEE Computer, 30(9):46-48, September 1997.

- [5] Greg Buzzard, et al. Hamlyn: a high-performance network interface with sender-based memory management. HP Laboratories Technical Report HPL-95-86, August 1995.

- [6] William J. Dally, et al. Retrospective: The J-Machine. In 25 Years of ISCA Selected Papers, 1998, pp. 54-58.

- [7] Al Davis, Mark Swanson, and Mike Parker. Efficient Communication Mechanisms for Cluster Based Parallel Computing. Communication, Architecture, and Applications for Network-Based Parallel Computing, 1997, pp. 1-15

- [8] Susan J. Eggers, et al. Simultaneous Multithreading: A Platform for Next-Generation Processors. IEEE Micro, 17(5):12-19, October 1997.

- [9] Thorsten von Eicken, et al. U-Net: A User-Level Network Interface for Parallel and Distributed Computing. In Proceedings of the 15th ACM SOSP, December 1995, pp. 40-53.

- [10] Thorsten von Eicken, et al. Active Messages: A Mechanism for Integrated Communication and Computation. In Proceedings of the 19th Annual ISCA, 1992, pp. 256-266

- [11] Marco Fillo, et al. The M-Machine Multicomputer. In Proceedings of the 28th Annual International Symposium on Microarchitecture, 1995, pp. 146-156.

- [12] Andrew Gallatin, Jeff Chase, and Ken Yocum. Trapeze/IP: TCP/IP at Near-Gigabit Speeds. In Proceedings of 1999 USENIX Annual Technical Conference, FREENIX Track, June 1999.

- [13] Dana S. Henry and Christopher F. Joerg. A Tightly-Coupled Processor-Network Interface. In Proceedings of the 5th International ASPLOS, October 1992, pp. 111-122.

- [14] Jeffrey Kuskin, et al. The Stanford FLASH Multiprocessor. In Proceedings of the 21st Annual ISCA, April 1994, pp. 302-313.

- [15] Richard P. Martin, et al. Effects of Communication Latency, Overhead, and Bandwidth in a Cluster Architecture. In Proceedings of the 24th Annual ISCA, June 1997, pp. 85-97.

- [16] Doug Matzke. Will Physical Scalability Sabotage Performance Gains? IEEE Computer, 30(9):37-39, September 1997.

- [17] Larry McVoy and Carl Staelin. Imbench: Portable Tools for Performance Analysis. In Proceedings of the USENIX 1996 Technical Conference, January 1996, pp. 279-294.

- [18] Shubhendu S. Mukherjee and Mark D. Hill. Making Network Interfaces Less Peripheral. IEEE Computer, 31(10), October 1998, pp 70-76.

- [19] V. S. Pai et al. RSIM: An Execution-Driven Simulator for ILP-Based Shared-Memory Multiprocessors and Uniprocessors. In Proceedings of the 3rd Workshop on Computer Architecture Education, 1997.

- [20] Scott Pakin, Vijay Karamcheti, and Andrew A. Chien. Fast Messages (FM): Efficient, Portable Communication for Workstation Clusters and Massively-Parallel Processors. IEEE Concurrency, vol 5, no. 2, April-June 1997, pp. 60-73.

- [21] Steven K. Reinhardt, James R. Larus, and David A. Wood. Tempest and Typhoon: User-Level Shared Memory. In Proceedings of the 21st Annual ISCA, 1994, pp. 325-336.

- [22] Lambert Schaelicke. Architectural Support for User-Level I/O. Ph.D. Dissertation, University of Utah, 2001.

- [23] Mark Swanson, et al. Message Passing Support in the Avalanche Widget. Technical Report UUCS-96-002, University of Utah, March 1996.

- [24] Dean M. Tullsen, et al. Supporting Fine-Grained Synchronization on a Simultaneous Multithreading Processor. In Proceedings of the 5th HPCA, January 1999.

- [25] InfiniBand Trade Association. http://www.infinibandta.org.

- [26] International Technology Roadmap for Semiconductors. Semiconductor Industry Assoc., 1998.

- [27] Motorola Semiconductor Product Sector. RapidIO: An Embedded System Component Network Architecture. February 22, 2000.

## A Binary Translation System for Multithreaded Processors and its Preliminary Evaluation

## Kanemitsu Ootsu, Takashi Yokota, Takafumi Ono, and Takanobu Baba

Department of Information Science, Faculty of Engineering, Utsunomiya University 7-1-2 Yoto, Utsunomiya-shi, Tochigi, 321-8585 Japan. phone&fax: +81-28-689-{6284, 6290} e-mail: {kim, yokota}@is.utsunomiya-u.ac.jp

#### Abstract

Thread level parallelism (TLP) is a key technology to coming generation of high performance processors. Although it provides higher processing capability, the loss of compatibility with existing processors is a crucial issue. This research is motivated by the following two points: (1) TLP requires multithread programming which is rather difficult for ordinary programmers, or complexed compilation technologies that can exploit multithread parallelism, and (2) existing binary codes should be executed efficiently on multithreaded processors. In this paper, we first propose a binary translation system, that translates existing binary codes to multithreaded ones and optimizes them dynamically during execution. The system inputs the original binary codes and translates them to internal RTL representation. It analyzes the structure of the program and applies multithreading to loop bodies in a thread pipelining manner. A pilot binary translator, that is a part of the proposed system, was built for the sake of preliminary evaluation. Evaluation results illustrate effectiveness of the system.

Keywords: binary translation, thread level parallelism, multithreading, thread pipelining, run-time optimization.

## 1 Introduction

Thread level parallelism (TLP) is one of the most promising key issue to high-performance processor architecture in the next generation. Present state-of-the-art technologies, such as superscalar, out-of-order, speculative execution, and value prediction, are successful in keeping continuous compatibility with conventional processor's instruction set architecture (ISA). And even in different architectures, i.e., VLIW (very long instruction word), a sort of binary translation technology is adapted so that the processor looks like conventional ISA from users view.

On the other hand, TLP essentially requires multithreaded machine codes to exploit full ability of the architecture. Because of the discontinuity of binary code compatibility, we can find the following two problems.

First, who (what) can produce multithreaded codes? Most programmers are not so skilled to make their application fully multithreaded. To this problem, further compiler technologies are required for automatic multithreading of an original application program in the near future. Second one is rather practical, i.e., we should abandon plenty of existing (single-thread) binary codes if their source codes are not available. The single-thread binary codes could run on multithreaded processors, although, they can receive no performance gain from TLP. Thus these two problems prevent TLP from being widely accepted. As a realistic solution to the problems, we focus our approach on the efficient reuse of existing binary codes on a multithreaded architecture that exploits rich TLP.

In this paper, we propose a binary translation and run-time optimization system.[14, 15] We first introduce binary translation technology that translates existing single-thread code to multithreaded ones. Source binary codes are analyzed, decomposed into threads, and then mapped onto the target architecture.

We then introduce dynamic (run-time) optimization of the translated codes. Because of lack of source code information, static analysis has some limitations: e.g., distinction of instruction words and data is not clear, and the target addresses of indirect jumps remain unknown.

The rest of this paper is organized as follows. We first discuss design principles to realize our ideas in Section 2, where we make some basic assumptions and discuss system requirements. Then we propose a binary translation and optimization system in Section 3, where basic components and their functions are discussed. Section 4 describes static optimizer in detail and Section 5 shows the preliminary evaluation. Section 6 presents related works which aim at binary translation or optimization. This section clarifies the standpoint of the proposed system and thus its unique features. Finally, we conclude this paper in Section 7.

## 2 Design Principles

## 2.1 Multithreading by the Thread Pipelining Model

In order to run a single-thread binary code efficiently on a multithreaded processor, logical structure embedded within the source binary code is extracted and the program is restructured to a set of threads. For the following discussion, we make an assumption on the target multithreaded architecture.

Needless to say, single-thread code follows a sequential programming manner. Although the ideal objective is to exploit all possible parallelism inherent in the program, it is not realistic for binary code inputs. We have started discussion with a simple idea: we payed our attention to *loop* structures.

The idea is very natural. A programmer tends to follow a sequential program (thread) depicted in a onedimensional space. In such situations, a parallel structure is expressed as a loop. In other words, a loop structure contains inherent parallelism. Thus, it is appropriate that each iteration in the loop is converted to a thread. In many cases, a loop structure contains many iterations, and thus enables us to exploit the maximum parallelism.

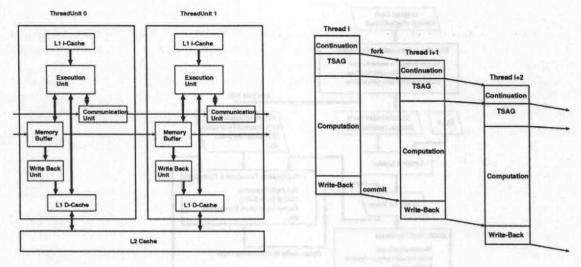

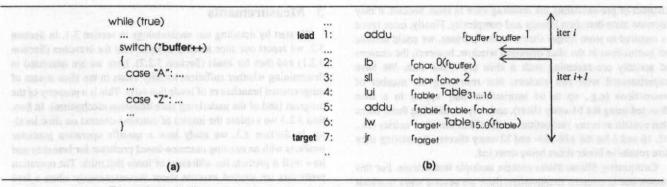

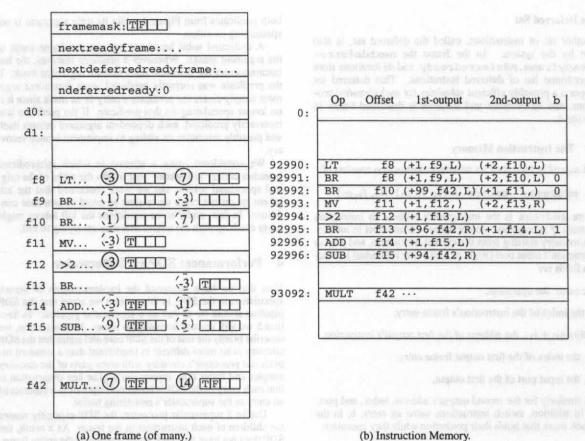

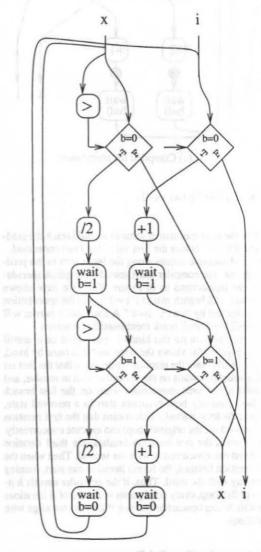

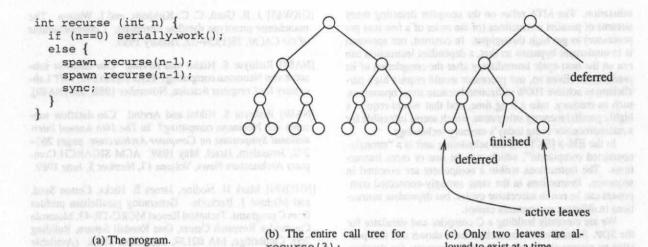

Thread pipelining model[1] best fits to our purpose described above. Figure 1 shows partial structure of the multithreaded processor based on the model. Each thread generated by binary translation is mapped to a thread execution unit in order. Communication unit and Memory Buffer handle inter-thread control and dependencies, respectively.

Basically, each iteration corresponds to a thread, and threads are executed in a pipeline manner. Figure 2 illustrates the thread pipelining[1]. Each thread consists of four stages: Continuation, Target Store Address Generation (TSAG), Computation, and Writeback.

The Continuation stage introduces loop variables and necessary data so as to be used in the thread. After the Continuation stage completes, the succeeding thread is invoked. The TSAG stage checks dependencies of shared data between threads. Addresses of shared data are notified to Memory Buffer, which detects access dependencies between threads by monitoring addresses. The Computation stage does the peculiar calculation assigned to the thread. After completing the Computation stage, a thread terminates its life in the Writeback stage. The Writeback stage cannot be started until the preceding threads' Writeback stages are completed.

## 2.2 Single- to Multi-thread Binary Translation

As described above, we have introduced a thread pipelining concept to our system. This pipelining is a fundamental requirement in the proposed system. It is totally different from existing translation systems in that it converts single-thread code to multithreaded one whereas others translate to single-thread. In other words, ordinal translators don't change program structure, although, our system should arrange the analyzed program structure to achieve the best fit to the thread pipelining model.

Source binary code is first analyzed with its logical structure, and the structure is re-organized following the thread pipeline manner. Then, target machine code is generated. During analysis of program structure (i.e., control- and data-flow) and re-configuration phase, abstract representation is required. We have introduced RTL (register transfer level) representation, which is used internally in the translator. Actual translation procedure is displayed in Section 3.

## 2.3 Necessity of Run-time Optimization

In principle, binary translator converts a loop structure to a set of threads. This requires accurate analysis of program structure, however, the translator could not find full information because of lack of source code information. For example, indirect branch hides the target address of iteration. So, some loop structures may

Figure 2: Thread Pipelining Model

remain unfound even when the analysis phase is completed. These loop structures cannot be converted to multithreaded code, and they do not appear until the translated codes run.

Thus, to exploit full parallelism of the program, it is necessary that behavior of the program is monitored and that 'hot' portion is translated to multithreaded code. This methodology is a kind of run-time optimization. Like the binary translation introduced in the previous section, run-time optimization requires re-structuring of the program (i.e., converting single-thread code to multithreaded one) where other run-time optimization techniques do not essentially affect program structure.

## **3** The Binary Translation and Optimization System

### 3.1 Systems Logical Structure

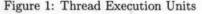

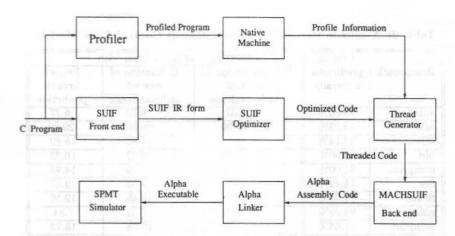

As discussed above, in order to execute existing binary codes on next-generation multi-threaded processor, the system requires following two phases: (i) binary translation and static optimization and (ii) run-time optimization. Figure 3 illustrates the configuration of the proposed system.

In Figure 3, STO (Static Translation and Optimizer) executes the phase (i) and DTO (Dynamic Translation and Optimizer) performs (ii). The figure includes Multithreaded Processor, whose basic architecture is described in Section 2.1 and Figure 1. The processor's basic ISA is not limited to some specific architecture since the original binary codes may be translated according to the target architecture by STO and DTO.

STO inputs the sequence of the source binary codes and translates them to the target binary code. If the program requires dynamic linked libraries (DLLs), STO prepares the necessary libraries and links. Resulting executable binary image is put into the main memory and the processor executes the executable.

During the processor executes the translated binary code, the behavior of program is monitored. We introduce profiling techniques for monitoring. We assume that the processor has additional mechanisms that reduce profiling overheads.

DTO uses the profiling information and observes actual behavior of the application program. When detecting a buried 'hot' loop, it begins binary translation and optimization. It substitutes the single-thread 'hot' part by the translated multithreaded code, and thus accelerates total execution.

## 3.2 Static Translation and Optimization (STO)

As shown in Figure 3, STO inputs the source binary code and translates it to multithreaded code. Once STO reads the source binary code, the code is translated into an internal representation. The representation is, in principle, abstracted in a machine independent RTL (register transfer level) form. The internal representation

Figure 3: Proposed System Diagram

enables STO to do powerful optimization as taken in ordinal compilers/optimizers. In the proposed system, STO generates threads in the internal representation level.

Basically, STO works before the program runs. Its mission is to prepare translated binary code for the multithreaded processor before the program is started, however, it could not complete the translation. The reason is that no clear distinction is made between instruction code and data and that run-time information is buried. For example, an indirect jump operation hides its branch target address and thus prevents further analysis. Another example is the self-modifying code that determines its own execution code at run-time, so STO cannot know exactly what is to be done in the program. The remaining translation should be done at run-time and DTO handles it.

During analysis of input binary code, STO acquires useful information: code analysis information, controland data-flow information. DTO does full use of these information. This reduces overheads in run-time optimization. STO inserts profiling codes so that DTO can collect proper information at low cost.

## 3.3 Dynamic Translation and Optimization (DTO)

DTO's major objective is run-time optimization (Figure 3). Unlike STO, DTO runs concurrently with the execution of application. It is invoked at proper intervals during application execution. DTO collects profiling information and monitors the program behavior. After detecting a hot-path, DTO arranges global scheduling, eliminates redundant codes, and applies possible optimization methods[2]. Then, DTO substitutes the original code to the optimized one.

Profiling codes are not removed by the DTO optimization. This means that profiling continues until the application is terminated. So DTO can apply further optimization incrementally and it can follow the change of program behavior. The DTO approach is similar to profile-guided compilation[3]. Since DTO can collect more detailed information, it should achieve deeper optimizations.

Source binary codes may contain self-modifying codes. STO cannot handle such codes since actual codes are determined at run-time. Thus, DTO should provide similar functions that STO does: i.e., the series of binary translation and optimization processes. Actually, input of source binary code, translation to internal representation, and control- and data-flow analysis should be processed by DTO. 16

## 4 Binary Translation Method

We have built an experimental binary translation software in order to estimate the effectiveness of the proposed system. The pilot translation system is to be a part of STO in the proposed system. This section introduces binary translation methods employed in the pilot system.

## 4.1 Basic Algorithm

As introduced in the previous section, the binary translator inputs binary codes and outputs multithreaded one. The translator performs the following steps:

- (1) inputs source binary code and translates to internal representation,

- (2) determines basic blocks, analyzes control-flow, and detects loop structure,

- (3) analyzes data-flow, detects loop variables and inter-loop dependencies,

- (4) converts loop structure to multithread codes in a thread pipelining fashion, and

- (5) generates target machine code from internal representation.

The translator reads the source binary code. It begins code analysis from the starting address specified in the binary code. Input code is translated into the internal representation in order.

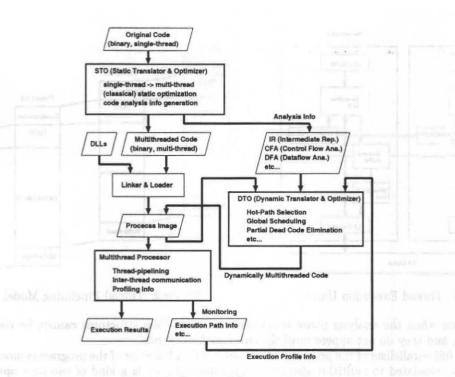

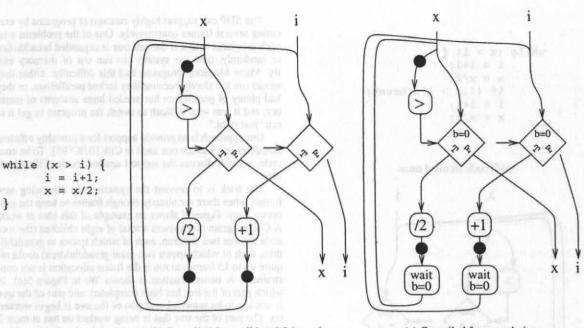

The internal representation categorizes instructions into six groups: alu operation, inter-register transfer, jump, branch, load/store, and other operations. Each instruction category has its unique operand expression. Figure 4 shows a part of instruction stream converted into the internal representation. The internal representation forms a list structure. Once the input binary codes are read and translated into the representation, succeeding processes, (2) to (5), are performed on the representation.

In the step (2), the translator determines basic blocks and analyzes control flow. It seeks back-edges, i.e., backward jumps/branches, in the internal representation. A back-edge is an important hint to mine a loop structure. The translator trys to find a path from the target address of a back-edge to the back-edge itself. If the path exists, it constitutes a loop structure.

In the step (3), the translator analyzes data-flow in the loop structure. It presumes loop variables used in the loop. The present pilot system finds the loop variables by increment of integer variables. The translator can analyze multiplexed loops.

The translator modifies the internal representation according to the result of multithreading operation (in the step (4)). Step (5) generates the target machine codes from the internal representation.

Next, we will explain step (4), the key part of the translator, in more detail.

In order to exploit sufficient parallelism by multithreading, we have found the following two requirements: (i) an interval of thread invocation should be shortened, and (ii) the synchronization time in resolving dependency should be reduced.

To solve (i), the Continuation stage prepares loop variables used in the succeeding thread. The values of loop variables are computed in the preceding thread. A newly created thread can start the execution of its loop body.

To reduce synchronization overheads due to inter-thread dependency (ii), the translator tries to move 'load' and 'store' instructions of shared data backward and forward in the Computation stage, respectively.

After the Continuation stage, addresses of inter-thread dependent data are registered in Memory Buffer in the TSAG stage. Execution of the consecutive TSAG stages cannot be overlapped since the stage determines shared data. Thus, at the entrance of the stage, the processor waits for completion signal from its preceding thread, and at the exit of the TSAG stage it sends completion signal to its succeeding thread. These inter-thread communications are handled by Communication Unit, shown in Figure 1.

Most calculations in the original loop body are executed in the Computation stage. Inter-thread dependencies are registered at the TSAG stage and Memory Buffer monitors all memory accesses. It handles inter-thread synchronization in a producer-consumer manner.

The Writeback stage writes calculation results onto memory. Since the resulting data should be stored in the semantic order, the stage cannot be overlapped between threads. Thus at the start-point of the stage, the processor should wait for a termination signal from its predecessor. After completion of this stage, the thread terminates.

5

Following the thread pipelining model, as shown in Figure 2, each thread consists of four stages. Three out of four stages cause overheads and only Computation stage performs the peculiar calculation in the iteration. Thus, to exploit sufficient performance on this model, the Computation stage should be long enough to hide overheads caused in other stages. We have introduced a loop unrolling technique as a solution. The succeeding section discusses the effectiveness.

Figure 4: Internal Representation Example

## 4.2 Translation Example

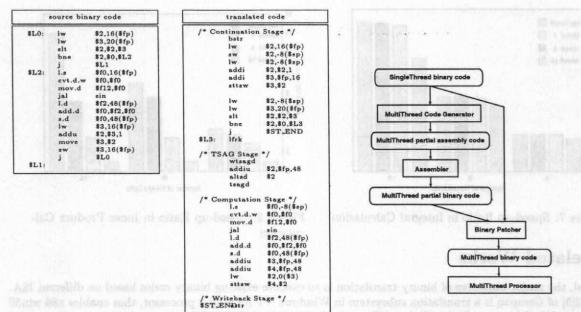

Figure 5 illustrates a simple example of translation. The instruction stream, listed in the left side, is a part of the source binary code (disassembled for display use). In our pilot translator, only a hot-path (i.e., loop) is translated to multithreaded code as described in Section 4. The right side list shows the translated output of the hot-path.

To avoid complexity in evaluation processes, the original ISA is extended by adding several thread control instructions so that the codes can be run on the target multithreaded architecture.

A thread pipeline begins with bstr instruction. In the Continuation stage, the thread calculates the loop variable used in its succeeding thread from its own variable (address (\$fp+16) in Figure 5), stores the result by sttsw instruction, and then generates the succeeding thread by lfrk. Note that a loop variable is accessed via (\$sp-8) in this example.

In the TSAG stage, dependent address of (\$fp+48) is registered to Memory Buffer by altsd instruction. For proper synchronization among neighboring threads, wtsagd and tsagd instructions are used.

We can find a load instruction that fetches data from (\$fp+48). When the instruction is executed, Memory Buffer detects the memory access and execution stalls until the preceding thread updates the data.

In the Writeback stage, estr instruction writes calculated data into memory and the thread terminates.

## 5 Preliminary Evaluation

## 5.1 Experimental Translation System

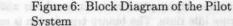

To evaluate the basic idea of binary translation to multithreaded codes and their optimization, we have built a pilot translation system. Figure 6 shows the block diagram. The objective of the system is to evaluate the STO functions which was described in Section 3.2. MultiThread Code Generator in Figure 6 follows all the translation steps (1) to (5) described in Section 4.1.

In Figure 6, MultiThread Code Generator translates source binary code to multithreaded one. Hot-path is manually guided to the translator for evaluation purpose. Resulting partial binary code is merged into the original (single-thread) binary code by **Binary Patcher**. Binary Patcher removes hot-spot codes from the riginal binary code, and inserts translated multithreaded code. Thus the hot-path is executed in the thread-pipelining manner and the rest of the program is executed in a single thread. At this timing, necessary run-time libraries are linked. Then, the prepared multithreaded binary code is executed in a simulator.

Figure 5: A Simple Example of Binary Translation

## 5.2 Evaluation Environment

We have assumed that the target multithreaded processor follows the architecture of SIMCA[4]. SIMCA is a simulator based on thread pipelining model and matches to our evaluation purpose.

Original binary codes are compiled by gcc cross compiler for SIMCA. The compiler's version is 2.7.2.3 and "-02" option is applied. Application programs are (a) integral calculation in a 'sin' trigonometric function using a trapezoidal equation and (b) inner product calculation.

Performance was measured as execution cycles of the hot-path by using the SIMCA simulator. Original binary code was executed on SIMCA and the number of execution cycles of the hot-path was measured. Similar evaluation was done for the translated code. By comparing the number of execution cycles, speed-up ratio was calculated.

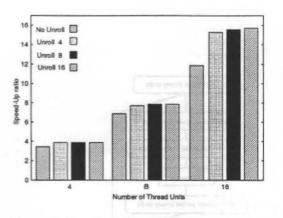

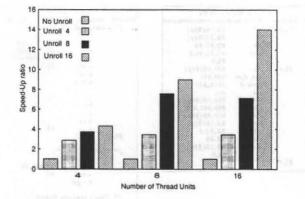

In this preliminary evaluation, the number of thread units were assumed to be 4, 8, and 16. Furthermore, the loop-unrolling technique was applied to each application program; the measured unrolling factors were 4, 8, and 16 and no unrolling was measured for comparison purpose.

## 5.3 Evaluation Results

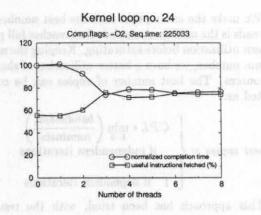

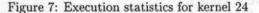

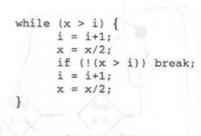

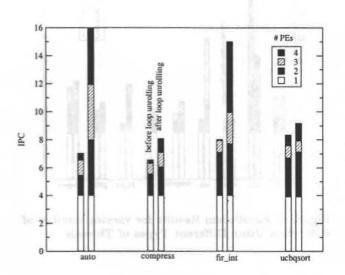

Figures 7 and 8 illustrate evaluation results for integral and inner product calculation applications, respectively.

In the integral calculation (Figure 7), the system gains performance linearly to the number of thread units. Unrolling factor does not affect the performance except 'no unroll' case.

In the inner product calculation (Figure 8), we can find that speed-up ratio is limited by unrolling factor. In 'no unroll' case, speed-up ratio is around 0.9 in spite of the number of thread units. We can find the similar phenomenon in the 'unroll 4' case. In the 'unroll 8' case, speed-up is achieved when 8 thread units are used. However, the performance saturates in the 16 thread units case. We can recognize linear speed-up in the 'unroll 16' case.

The integral calculation contains many operations enough to hide thread pipelining overheads. This leads near-linear speed-up according to the number of thread units.

On the other hand, the inner product calculation contains less operations than the integral calculation. Thus thread pipelining overheads could not be hidden unless sufficient loop-unrolling is applied.

These results reveal that efficiency in thread pipelining heavily depends on the grain size of calculation.

7

20

Figure 7: Speed-up Ratio in Integral Calculation

Figure 8: Speed-up Ratio in Inner Product Calculation

## 6 Related Works

In general, the major objective of binary translation is to execute existing binary codes based on different ISA.

FX!32[5] of Compaq is a translation subsystem in Windows NT for Alpha processor, that enables x86 win32 codes to run on Alpha platforms. It emulates x86 instructions and does binary translation into Alpha ISA codes. During idle time, The binary translation is executed with profiling results from the preceding emulation. Once the code is translated, the resulting native code is executed and earns high performance.

DAISY[6] of IBM translates well-used ISA codes, such as PowerPC and x86, so that programs run on the original VLIW processor. The system exploits instruction level parallelism (ILP). It does no emulation.

Transmeta's Crusoe[7] has similar mechanism to DAISY. Crusoe is based on VLIW and it has unique ISA. The processor runs CMS (Code Morphing Software) and the software dynamically translates x86 instructions to its internal ones. Different from DAISY, CMS translates only hot-spot codes and takes incremental optimization concurrently with program execution.

These systems listed above are for translation purpose into different ISA. Following systems aims at optimization.

Dynamo[8] of Hewlett-Packard translates PA-RISC binaries to PA-RISC codes for optimization purpose. Dynamo translates concurrently with emulation of PA-RISC instructions. From profiling results of emulation, it can find hot-spots and translates into optimized codes. The resulting codes are cached, thus, once the hot-spot is translated, the optimized codes are executed for acceleration.

Morph[9] of Harvard University does profiling under the cooperation with operating system, and it optimizes executed codes off-line using the results of profiling.

Deco[10] of Harvard University does run-time optimization and binary translation. Deco can re-translate optimized codes according to change of the program's behavior.

BOA[11] of IBM focuses EPIC-style approach, that aims at high clock frequency by simplified hardware, abandoned out-of-order superscalar mechanisms like PowerPC. BOA optimizes instruction scheduling for such architecture by using binary translation technology. Where DAISY translates only once, BOA continuously monitors the behavior of execution paths and does run-time optimization.

Java's HotSpotVM[12] collects profile information during interpretive execution. When it detects a hotspot, the hot codes are translated into native codes. The VM uses the translated binaries so that it accelerates performance.

UQBT[13] is a framework of retargetable binary translation. The system's unique point is that, theoretically, it enables any ISA codes translated into any other ISA. Currently it supports SPARC, x86, and Java bytecode.

All systems shown above assume single-thread code and none aims at performance enhancement by multithreading.

## 7 Concluding Remarks

In this paper, we proposed a binary translation and optimization system that enables existing binary codes to run on the future multithreaded processors. We first discussed about the basic assumption on the target architecture and the essential requirements for single-thread binary codes to be translated to multithreaded codes.

The proposed system roughly consists of static translator and optimizer (STO) and dynamic translator and optimizer (DTO). STO initially translates an input binary code to the multithreaded one. DTO handles the dynamic behavior of the translated program and optimizes according to profiling results at run-time.

A pilot binary translator was built for the sake of preliminary evaluation. Programs used for evaluation are integral calculation in a *sin* trigonometric function using a trapezoidal equation and inner product calculation. The results show overheads in thread pipelining and, if each thread has sufficient calculation, the overhead can be negligible and the speed-up, linear to the number of thread units, is achieved.

At the present time, DTO is not completed. We will continue to develop the proposed system and show effectiveness in practical programs such as SPEC benchmarks.

Acknowledgement This research was supported in part by the Grant-in-Aid for Scientific Research (C) of Japan Society for Promotion of Science (JSPS) No.12680328.

## References

- J. Y. Tsai, J. Huang, and et al., "The Superthreaded Processor Architecture," IEEE Transactions on Computers, Special Issue on Multithreaded Architectures, Vol. 48, No. 9, 1999.

- [2] D. F. Bacon, S. L. Graham and O. J. Sharp, "Compiler Transformations for High-Performance Computing," ACM Computing Surveys, Vol. 26, No. 4, pp. 345–420, 1994.

- [3] M. D. Smith, "Overcoming the Challenges to Feedback-Directed Optimization," Proceedings of ACM SIG-PLAN Workshop on Dynamic and Adaptive Compilation and Optimization (Dynamo'00), 2000.

- [4] J. Huang. "The SImulator for Multi-threaded Computer Architecture(SIMCA), Release 1.2.," http://www-mount.cs.umm.edu/Research/Ag-assiz/simca.html.

- [5] R. J. Hookway and M. A. Herdeg, "DIGITAL FX!32: Combining Emulation and Binary Translation," Digital Technical Journal, Vol.9, No 1, pp. 3-12, 1997.

- [6] K. Ebcioglu, E. R. Altman, "DAISY: Dynamic Compilation for 100% Architectural Compatibility," Proceedings of 24th Annual International Symposium on Computer Architecture, pp. 26-37, 1997.

- [7] A. Kaliber, "The Technology Behind Crusoe Processors," 2000, URL: http://www.transmeta.com/crusoe /download/pdf/crusoetechwp.pdf.

- [8] V. Bala, E. Duesterwald, S. Banerji, "Dynamo: A Transparent Dynamic Optimization System," Proceedings of Programming Language Design and Implementation, 2000.

- [9] X. Zhang, Z. Wang, and et al., "System Support for Automatic Profiling and Optimization," Proceedings of 16th Symposium on Operating Systems Principles, 2000.

- [10] E. Feigin, "A Case for Automatic Run-Time Code Optimization," Senior thesis, Harvard College, Division of Engineering and Applied Sciences, 1999.

- [11] S. Sathaye, P. Ledak, and et al., "BOA: Targeting Multi-Gigahertz with Binary Translation," Workshop on Binary Translation (Binary 99), 1999.

- [12] Sun Microsystems, "Java HotSpotTM Technology," URL: http://java.sun.com/products/hotspot/

- [13] C. Cifuentes and M. Van Emmerik, "UQBT: Adaptable Binary Translation at Low Cost," Computer, Vol. 33, No. 3, pp. 60–66, 2000.

- [14] K. Ootsu, T. Ono, T. Baba, "A Methodology for Multithreading with Binary Translation," IPSJ SIG Notes, Vol.2001, No.10, pp.41-46, January 2001 (in Japanese).

- [15] T. Ono, K. Ootsu, T. Yokota, T. Baba, "Preliminary Evaluation of Binary-Level Multithreading," IPSJ SIG Notes, Vol.2001, No.76, pp.183–188, August 2001 (in Japanese).

## service of a graduate see

to data papan wangopowit a kiineya tewale da en na usa wa the fiterro moltificiodoo processori da peringeruno wat the common bandromone as to walay

(a) The structure of plantarian agreeding processing of the structure of the plantarian distribution UTR (OTT) transmission of the structure of the structur

(a) any property distances with the analytical end of a set of the second se

## septremeters.

- (4) F. Yaali, h. Baarg, and et al., "The Tra-Computers, found from on Multillier and

- M. E. Sandel, "Orstronging the Challen at Physics Workshot on Dynamic and Advance Physics Workshot on Dynamics and Advance

- (4) J. Hump, "The Straphone for Volumeter to constant of the second of Competer Account."

- [3] B. J. Howlender and M. A. Rusley, 'F Digital Tradition Journal, Vol. 5, No. 1.

- [4] K. Ebriegh, R. A. Akman, "DAPN ...

- [7] A. Kollins, "The Technology Keiting, C. R. Dor research and Provident Mark Landschol,"

- [8] V. Dela, E. Duoshir end. S. Ban El, "We et Print constant formation Descent and a statistical community.

- [0] K. Zhunu, Z. Wang, and et al., "Spatiat... of DBE Spreastern an Operation System 1.

- [4] S. Feigle, "A Gam for Automatic Rate 1 (c) of Distributing and Applied Sciences, 1998.

- M. Sadinerr, P. Ledak, and et al., "BOA"

an Interve Pranslation (Thurst) (00) (1990)

- of ended hitting coalities it was seen that the head for

- [10] C. Citaresta and M. Yad Ehmundl, "UOP2 3 33, No. 5, 86, 80-86, 2000.

- [4] K. Goren, T. Grey, T. Baha, A. Massani, et Water Vol(200), Nul.0, ppello-66, huma-g

- [4] T. Giro, K. Gamer, T. Telaha, T. Baha, "Preprintic presentation of Proceedings, Texas, 1984, New York2001, Phys. Rev. Lett. Academic True in Japanese.", New York2001, Phys. Rev. Lett. Academic True in Japanese.

interfect a metric that etables consider binacy codes identified a front that bits construction on the targets also seen as a basic construction to matrificewised and translated to be translated to matrificewised.

in a strengt (STO) and dynamic translator and

Fregrams und für välunden om den välunden för av elt-tyngener und timer produce in tinden, ere en ellentrikken skandaufon skan zum

weak has no ever comparts for significant and

in stratter Aul for Scientific Research (C) of

A culterture," IEEE Dynamichum en <sup>2</sup>, 1999.

as a bill finite or, Press Science ACM 310and Determined Dynamic 1991, 1991.

have superfitMCA). Release 1.2 ? with/www.e

", itereitation and Eliser, "ranalintica,"

Provide the state of the second for an utility," Proregently declaration, pp. 7 517.

Research more investigation of Automatical and the second

and a state of the second state of the second

moto. And a later of the second second

Columbration with Blump, Travel dense, Workshop

And description of the state of

<sup>1</sup> Condition with triping Translation," JPRJ 247 1 areas

## The Predictability of Computations that Produce Unpredictable Outcomes

Tor Aamodt

Andreas Moshovos

Paul Chow

Department of Electrical and Computer Engineering University of Toronto {aamodt, moshovos, pc}@eecg.toronto.edu

#### Abstract

We study the dynamic stream of slices that lead to branches that foil an existing branch predictor and to loads that miss and measure whether these slices exhibit locality (i.e. repetition). We argue that this regularity can be used to dynamically extract slices for an operation-based predictor that speculatively pre-computes a load address or branch target (i.e. an outcome) rather than directly predicting the outcome based upon the history of outcomes. We study programs from the SPEC2000 suite and find they exhibit good slicelocality for these problem loads and branches. Moreover, we study the performance of an idealized operation-based predictor (it can execute slices instantaneously). We find that it interacts favorably with an existing sophisticated outcome-based branch predictor, and that slice-locality provides good insight into the fraction of all branch mispredictions it can potentially eliminate. Similar observations hold for operation-based prefetching of loads that miss. On average slice locality for branches and loads was found to be above 64% and 76% respectively when recording the 4 most recent unique slices per branch or load over a window of 64 committed instructions, and close to 61% and 73% for branches and loads respectively when we look at slices over a window of up to 128 committed instructions. The idealized operation predictor was found to correct approximately 68% of branch mispredictions or prefetch about 67% of loads that miss respectively (slices detected over a window of 64 instructions). At the same time, on average, the branch operation predictor mispredicts less than 0.6% of all branches that are correctly predicted by an existing branch predictor.

## **1** Introduction

Recently, the prospect of generalized operation-prediction has been raised as a way of boosting accuracy over existing outcomebased predictors. In operation prediction we guess a sequence of operations, or a computation slice that can be used to pre-compute a performance critical outcome (e.g., load address or branch target). This is in contrast to outcome-based predictors that directly predict outcomes exploiting regularities in the outcome stream. Since operation prediction does not require any regularity in the outcome stream, it has the potential of predicting outcomes that foil existing outcome-based predictors (in section 2, we provide an example that illustrates the potential of operation prediction).

Several recent proposals have shown that *slice-based precomputation* (the mechanism operation-prediction uses for predicting outcomes) can be used to successfully prefetch memory data, and may potentially be used to pre-compute hard to predict branches [4,9,15,16,10,11,12,17]. In this work, we study program behavior to understand *why operation-prediction works or may work* for predicting otherwise hard to predict program events.

We build on the experience with outcome-history-based dynamic prediction and study whether typical programs exhibit the behavior necessary for operation history-based prediction to be successful. We explain that, in a way that parallels outcome-based prediction, operation predictors can be built to exploit regularities in the operation (i.e., computation) stream. For example, previous work has shown that sufficient locality, or repetition exists in the value stream of many programs. This program characteristic is what facilitates outcome-based value prediction. In this work we study a set of programs from the SPEC2000 suite to determine whether sufficient repetition exists in the slices used to calculate performance critical outcomes that otherwise foil existing outcome-based predictors. This program characteristic is necessary (but not sufficient as we explain in section 2) if history-based operation prediction is to be successful. We restrict our attention to mispredicted branches and to loads that miss and study how much repetition, or locality exists in the operation streams that lead to them. To the best of our knowledge, no previous work on the dynamic locality characteristics of such slices exist. With few exceptions and as we explain in section 4, related proposals approach slice pre-execution as an alternate execution model, where the compiler orchestrates slice generation and pre-execution. While compiler directed slice pre-execution is an interesting and viable option, dynamic slice detection and execution can have its own advantages (e.g., binary compatibility). Accordingly, we believe it is an important alternative that deserves attention.

Our study provides the foundation necessary for understanding whether programs exhibit some of the behavior necessary for operation prediction. Moreover, our results provide insight on what kind of operation predictors we should be considering if we are to achieve a desired accuracy and coverage. For example, our study shows how successful a *last-operation* predictor can potentially be or whether *pattern-based operation* predictors may be necessary. A *last-operation* prediction would simply record the slice used to calculate a branch or load and use it the next time around to pre-calculate the branch or the load address. Such a predictor can be successful only if slices tend to repeat multiple times. Alternatively, a pattern-based operation predictor can exploit patterns in slice occurrence, e.g., slice S1 appears always after slice S2, and so on. While more complex, a pattern-based operation predictor could offer better accuracy and coverage over a last-operation one. How-

1

ever, in this work we restrict our attention to analyzing the potential of operation prediction. Specifically, the predictors we studied precompute their slices instantaneously. An actual predictor would require some time to execute through the predicted slice, hence it may not be able to pre-execute the slice early enough for prediction purposes. Further work is necessary to determine whether this is possible. Yet, in previous work we have shown that a simple predictor for loads that miss can successfully pre-execute loads that miss often for a set of pointer-intensive applications [9].

Our results indicate that performance critical slices exhibit high locality, more so for loads that miss. In particular, we find that average slice locality for branches and loads is above 64% and 76% when we record up the 4 most recent slices per branch or load respectively over a window of 64 committed instructions and close to 61% and 73% for branches and loads respectively when we look at slices over a window of up to 128 committed instructions. Our idealized operation predictor can correctly predict about 68% of mispredicted branches and accurately prefetch 67% of loads that miss (slices detected over a window of 64 instructions). At the same time, on the average the branch operation predictor mispredicts less than 1% of all branches that are correctly predicted by an existing branch predictor. Overall, we find that coverage (e.g., the fraction of branches that get a correct prediction from the operation predictor but an incorrect prediction from the existing outcome-based predictor) is highly correlated to the locality exhibited by the corresponding slices.

The rest of this paper is organized as follows. Section 2 reviews operation prediction, how it relates to outcome-based prediction, and the various choices existing when dynamically extracting slices. Section 3 presents our locality and accuracy results. In Section 4, we discuss related work explaining how operation prediction relates to other recently proposed slice-based execution models. Finally, Section 5 summarizes our findings and offers concluding remarks.

## 2 Operation Prediction Basics

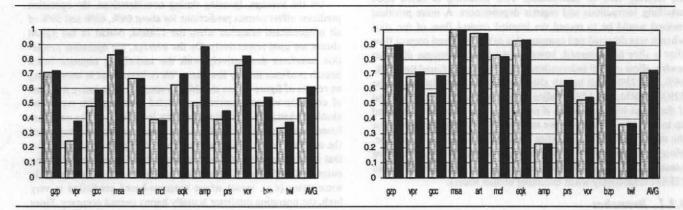

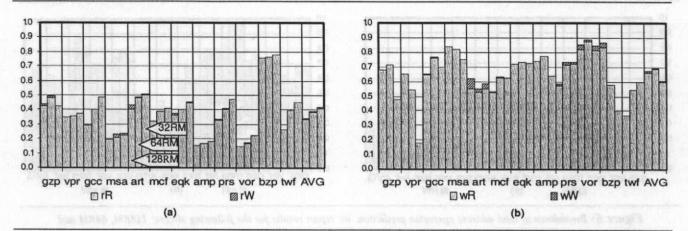

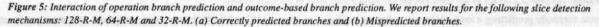

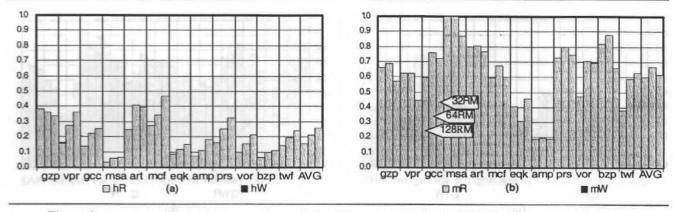

In this section we review operation prediction, explain how it relates to existing outcome-based predictors, and discuss what requirements exist for operation prediction to be successful. In section 2.1, we discuss some of the choices that exist in dynamically extracting slices and explain the choices made for the purposes of our study.